DDR5 वर डेटा सेंटर स्थलांतर इतर अपग्रेडपेक्षा अधिक महत्त्वाचे असू शकते.तथापि, बरेच लोक फक्त अस्पष्टपणे विचार करतात की DDR5 पूर्णपणे DDR4 पुनर्स्थित करण्यासाठी एक संक्रमण आहे.DDR5 च्या आगमनाने प्रोसेसर अपरिहार्यपणे बदलतात आणि त्यांच्याकडे काही नवीन असतीलस्मृतीइंटरफेस, जसे की SDRAM वरून DRAM अपग्रेडच्या मागील पिढ्यांमध्ये होतेDDR4.

तथापि, DDR5 हा केवळ इंटरफेस बदल नाही तर तो प्रोसेसर मेमरी सिस्टमची संकल्पना बदलत आहे.खरं तर, सुसंगत सर्व्हर प्लॅटफॉर्मवर अपग्रेडचे समर्थन करण्यासाठी DDR5 मधील बदल पुरेसे असू शकतात.

नवीन मेमरी इंटरफेस का निवडावा?

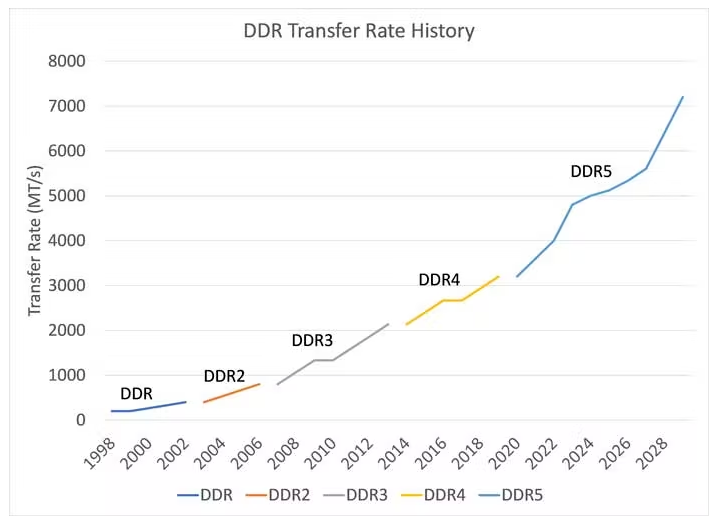

संगणकाच्या आगमनानंतर संगणकीय समस्या अधिक जटिल झाल्या आहेत आणि या अपरिहार्य वाढीमुळे मोठ्या संख्येने सर्व्हर, सतत वाढत जाणारी मेमरी आणि स्टोरेज क्षमता आणि उच्च प्रोसेसर क्लॉक स्पीड आणि कोर काउंट्सच्या रूपात उत्क्रांती झाली आहे, परंतु स्थापत्यशास्त्रीय बदलांना देखील चालना मिळाली आहे. , नुकत्याच वेगळ्या आणि अंमलात आणलेल्या AI तंत्रांचा अवलंब करण्यासह.

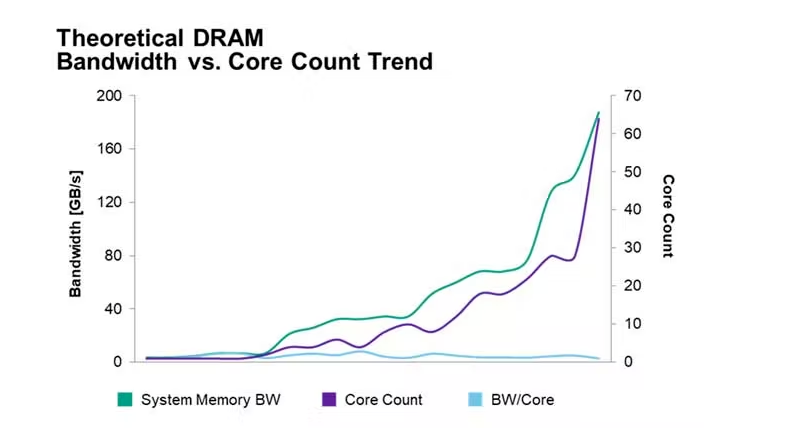

काहींना वाटेल की हे सर्व एकत्रितपणे घडत आहेत कारण सर्व संख्या वाढत आहेत.तथापि, प्रोसेसर कोरची संख्या वाढली असताना, डीडीआर बँडविड्थने गती ठेवली नाही, त्यामुळे प्रति कोर बँडविड्थ प्रत्यक्षात कमी होत आहे.

विशेषत: HPC, गेम्स, व्हिडीओ कोडिंग, मशीन लर्निंग रिझनिंग, बिग डेटा अॅनालिसिस आणि डेटाबेससाठी डेटा सेटचा विस्तार होत असल्याने, CPU मध्ये अधिक मेमरी चॅनेल जोडून मेमरी ट्रान्सफरची बँडविड्थ सुधारली जाऊ शकते, परंतु हे अधिक ऊर्जा वापरते. .प्रोसेसर पिन संख्या देखील या दृष्टिकोनाची टिकाऊपणा मर्यादित करते आणि चॅनेलची संख्या कायमची वाढू शकत नाही.

काही ऍप्लिकेशन्स, विशेषत: उच्च-कोर उपप्रणाली जसे की GPUs आणि विशेष AI प्रोसेसर, एक प्रकारचा उच्च-बँडविड्थ मेमरी (HBM) वापरतात.तंत्रज्ञान 1024-बिट मेमरी लेनद्वारे स्टॅक केलेल्या DRAM चिप्सपासून प्रोसेसरपर्यंत डेटा चालवते, ज्यामुळे ते AI सारख्या मेमरी-केंद्रित ऍप्लिकेशन्ससाठी एक उत्तम उपाय बनते.या अनुप्रयोगांमध्ये, जलद हस्तांतरण प्रदान करण्यासाठी प्रोसेसर आणि मेमरी शक्य तितक्या जवळ असणे आवश्यक आहे.तथापि, ते अधिक महाग आहे, आणि चिप्स बदलण्यायोग्य/अपग्रेडेबल मॉड्यूलवर बसू शकत नाहीत.

आणि DDR5 मेमरी, जी या वर्षी मोठ्या प्रमाणावर आणली जाऊ लागली, प्रोसेसर आणि मेमरी दरम्यान चॅनल बँडविड्थ सुधारण्यासाठी डिझाइन केली गेली आहे, तरीही अपग्रेडेबिलिटीला समर्थन देते.

बँडविड्थ आणि विलंब

डीडीआर 5 चा हस्तांतरण दर डीडीआरच्या कोणत्याही मागील पिढीपेक्षा वेगवान आहे, खरं तर, डीडीआर 4 च्या तुलनेत, डीडीआर 5 चा हस्तांतरण दर दुप्पट आहे.DDR5 ने अतिरिक्त आर्किटेक्चरल बदल देखील सादर केले आहेत ज्यामुळे साध्या नफ्यावर या हस्तांतरण दरांवर कार्यप्रदर्शन सक्षम होईल आणि निरीक्षण केलेल्या डेटा बस कार्यक्षमतेत सुधारणा होईल.

याव्यतिरिक्त, प्रत्येक मॉड्यूलला दोन स्वतंत्र उप-चॅनेल असण्याची परवानगी देऊन, BL8 ते BL16 पर्यंत बर्स्टची लांबी दुप्पट केली गेली आणि सिस्टममधील उपलब्ध चॅनेल अनिवार्यपणे दुप्पट केली गेली.तुम्हाला केवळ उच्च हस्तांतरण गती मिळत नाही, तर तुम्हाला एक पुनर्निर्मित मेमरी चॅनेल देखील मिळतो जो उच्च हस्तांतरण दरांशिवाय देखील DDR4 पेक्षा जास्त कामगिरी करतो.

मेमरी-केंद्रित प्रक्रियांना DDR5 मधील संक्रमणापासून खूप मोठी चालना मिळेल आणि आजचे अनेक डेटा-केंद्रित वर्कलोड्स, विशेषत: AI, डेटाबेस आणि ऑनलाइन व्यवहार प्रक्रिया (OLTP) या वर्णनात बसतात.

ट्रान्समिशन रेट देखील खूप महत्वाचा आहे.DDR5 मेमरीची सध्याची गती श्रेणी 4800~6400MT/s आहे.तंत्रज्ञान जसजसे परिपक्व होत जाईल तसतसे प्रसारण दर अधिक असणे अपेक्षित आहे.

उर्जेचा वापर

DDR5 DDR4 पेक्षा कमी व्होल्टेज वापरते, म्हणजे 1.2V ऐवजी 1.1V.जरी 8% फरक फारसा वाटत नसला तरी, वीज वापर गुणोत्तर, म्हणजे 1.1²/1.2² = 85% मोजण्यासाठी वर्ग केला जातो तेव्हा फरक स्पष्ट होतो, जे वीज बिलावर 15% बचत करते.

DDR5 द्वारे सादर केलेले वास्तुशास्त्रीय बदल बँडविड्थ कार्यक्षमता आणि उच्च हस्तांतरण दर ऑप्टिमाइझ करतात, तथापि, तंत्रज्ञान वापरल्या जाणार्या अचूक ऍप्लिकेशन वातावरणाचे मोजमाप केल्याशिवाय या संख्यांचे प्रमाण निश्चित करणे कठीण आहे.परंतु नंतर पुन्हा, सुधारित आर्किटेक्चर आणि उच्च हस्तांतरण दरांमुळे, अंतिम वापरकर्त्याला डेटाच्या प्रति बिट उर्जेमध्ये सुधारणा जाणवेल.

याव्यतिरिक्त, डीआयएमएम मॉड्यूल स्वतःहून व्होल्टेज समायोजित करू शकते, ज्यामुळे मदरबोर्डच्या वीज पुरवठ्याच्या समायोजनाची आवश्यकता कमी होऊ शकते, ज्यामुळे अतिरिक्त ऊर्जा-बचत प्रभाव मिळतो.

डेटा सेंटरसाठी, सर्व्हर किती उर्जा वापरतो आणि शीतकरण खर्च किती चिंताजनक आहे आणि जेव्हा या घटकांचा विचार केला जातो, तेव्हा अधिक ऊर्जा-कार्यक्षम मॉड्यूल म्हणून DDR5 निश्चितपणे अपग्रेड करण्याचे एक कारण असू शकते.

त्रुटी सुधारणे

DDR5 मध्ये ऑन-चिप त्रुटी सुधारणे देखील समाविष्ट आहे, आणि DRAM प्रक्रिया कमी होत असल्याने, बरेच वापरकर्ते सिंगल-बिट त्रुटी दर आणि एकूण डेटा अखंडता वाढविण्याबद्दल चिंतित आहेत.

सर्व्हर ऍप्लिकेशन्ससाठी, ऑन-चिप ECC DDR5 वरून डेटा आउटपुट करण्यापूर्वी रीड कमांड दरम्यान सिंगल-बिट त्रुटी सुधारते.हे सिस्टमवरील भार कमी करण्यासाठी सिस्टम सुधारणा अल्गोरिदमपासून DRAM वर ECC ओझे उतरवते.

DDR5 त्रुटी तपासणे आणि सॅनिटायझेशन देखील सादर करते आणि सक्षम असल्यास, DRAM डिव्हाइस अंतर्गत डेटा वाचतील आणि दुरुस्त केलेला डेटा परत लिहतील.

सारांश द्या

DRAM इंटरफेस सामान्यत: अपग्रेडची अंमलबजावणी करताना डेटा सेंटरने विचारात घेतलेला पहिला घटक नसला तरी, DDR5 जवळून पाहण्यास पात्र आहे, कारण तंत्रज्ञान कार्यक्षमतेत मोठ्या प्रमाणात सुधारणा करताना पॉवर वाचवण्याचे वचन देते.

DDR5 हे एक सक्षम तंत्रज्ञान आहे जे लवकर दत्तक घेणार्यांना भविष्यातील कम्पोझेबल, स्केलेबल डेटा सेंटरमध्ये सुंदरपणे स्थलांतरित होण्यास मदत करते.IT आणि व्यावसायिक नेत्यांनी DDR5 चे मूल्यमापन केले पाहिजे आणि त्यांच्या डेटा सेंटर ट्रान्सफॉर्मेशन योजना पूर्ण करण्यासाठी DDR4 वरून DDR5 मध्ये कसे आणि केव्हा स्थलांतर करावे हे ठरवावे.

पोस्ट वेळ: डिसेंबर-15-2022